# FACULTY OF ENGINEERING AND TECHNOLOGY

# DEPARTMENT OF ELECTRICAL ENGINEERING

**B.E** (EEE)

**V - SEMESTER**

# MICROPROCESSOR AND MICROCONTROLLER LAB

Name..... Reg. No..... Semester.....Batch

# DEPARTMENT OF ELECTRICAL ENGINEERING

#### VISION

To develop the Department into a "Centre of Excellence" with a perspective to provide quality education and skill-based training with state-of-the-art technologies to the students, thereby enabling them to become achievers and contributors to the industry, society and nation together with a sense of commitment to the profession.

#### MISSION

- M1: To impart quality education in tune with emerging technological developments in the field of Electrical and Electronics Engineering.

- M2: To provide practical hands-on-training with a view to understand the theoretical concepts and latest technological developments.

- M3: To produce employable and self-employable graduates.

- M4: To nurture the personality traits among the students in different dimensions emphasizing the ethical values and to address the diversified societal needs of the Nation

M5: To create futuristic ambience with the state-of-the-art facilities for pursuing research.

|         | EECP 507 MICROPROCESSOR AND<br>MICROCONTROLLER LAB |                                                                                                          |  |         |  |

|---------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|---------|--|

| EXP. NO | DATE                                               | DATE EXPERIMENT NAME                                                                                     |  | REMARKS |  |

| 1       |                                                    | Study of 8085 Microprocessor<br>a) Finding out the largest and smallest<br>number<br>b) Sorting an array |  |         |  |

| 2       |                                                    | Study of 8051 Microcontroller<br>a) Arithmetic Operations<br>b) Code Conversion                          |  |         |  |

| 3       |                                                    | Study of 8097 Microcontroller<br>a)Arithmetic Operations<br>b)Logical Operations                         |  |         |  |

| 4       |                                                    | Study of Programmable Peripheral Interface 8255                                                          |  |         |  |

| 5       |                                                    | Serial Data Communication using USART 8251 and Timer 8253                                                |  |         |  |

| 6       |                                                    | Seven Segment LED Display using 8051<br>Microcontroller                                                  |  |         |  |

| 7       |                                                    | Stepper Motor Control using 8051<br>Microcontroller                                                      |  |         |  |

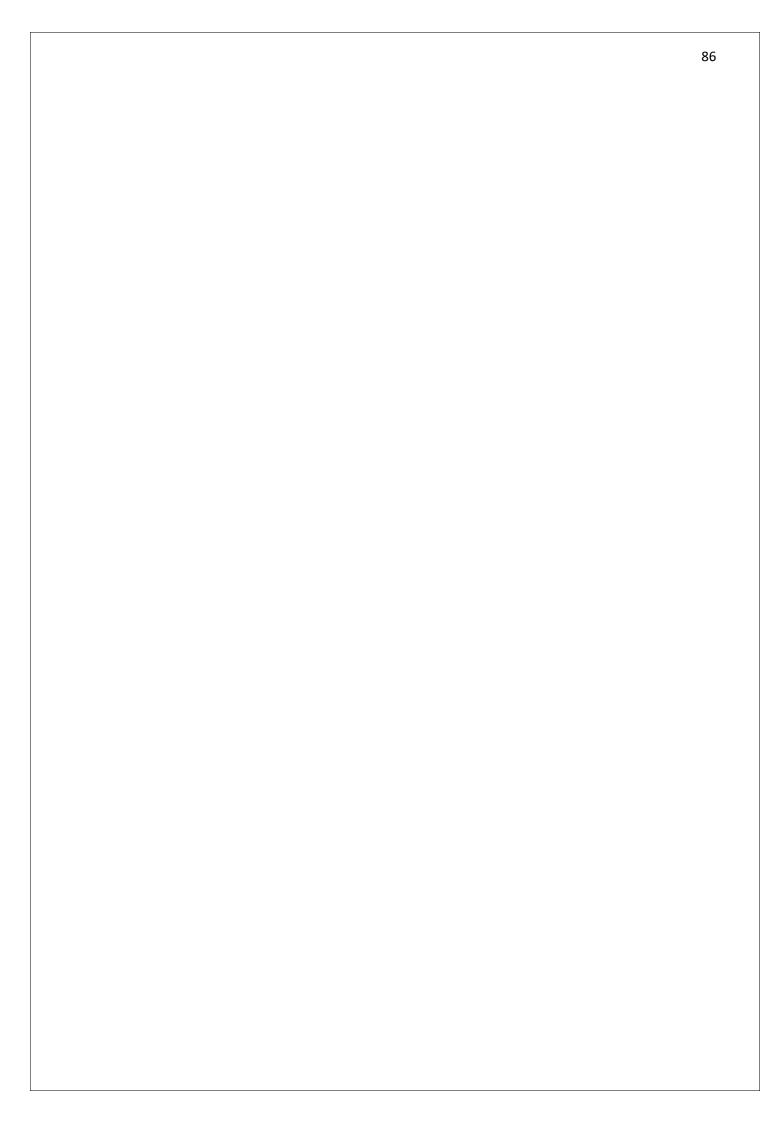

| 8       |                                                    | Study of Keyboard Display Interface 8279<br>using 8051 Microcontroller                                   |  |         |  |

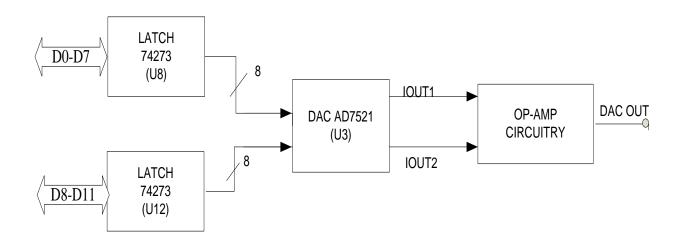

| 9       |                                                    | Applications of 8097 Microcontroller<br>a) DAC b) ADC c) PWM Generation                                  |  |         |  |

| 10      |                                                    | Serial Data Communication Between Two<br>8051 Kits                                                       |  |         |  |

# EX. No:

### DATE:

# STUDY OF 8085 MICROPROCESSOR

#### Aim

To study about the 8085 microprocessor and to execute the following programs on 8085 microprocessor kit.

- (i) To find the largest and smallest number in an array.

- (ii) To arrange the numbers in ascending and descending order.

#### Theory

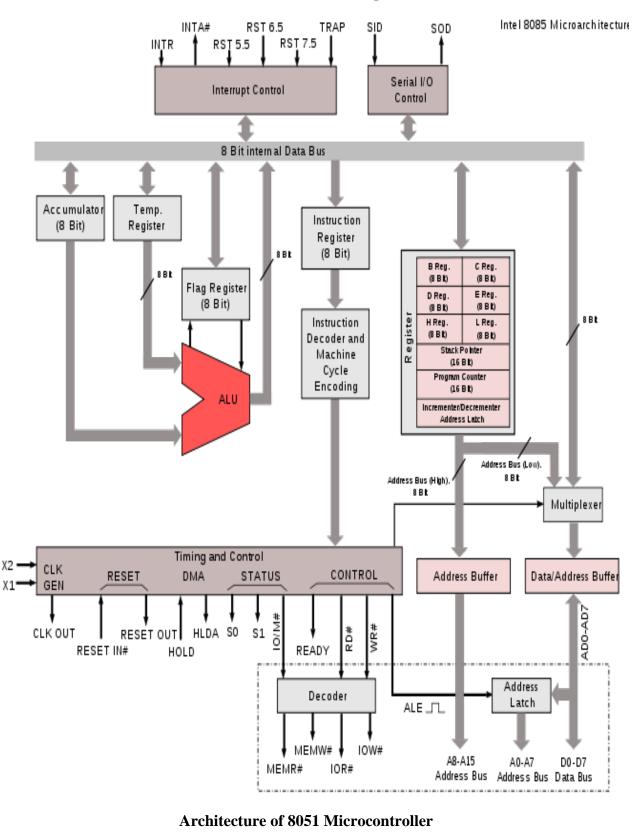

Intel 8085 is an 8-bit microprocessor. It is a 40 pin IC package. It uses a single +5v power supply. Its clock speed is about 3 MHz.

#### 8085 System Bus

A typical microprocessor communicates with memory and other devices (input and output) using three busses: Address Bus, Data Bus and Control Bus.

#### **Arithmetic Logic Unit (ALU)**

ALU performs the actual numerical and logic operation such as 'add', 'subtract', 'AND', 'OR' etc.

#### Registers

The 8085 microprocessor includes six registers, one accumulator, and one flag register. In addition, it has two 16-bit registers, the stack pointer and the program counter.

#### **Instruction Register/Decoder**

Latest instruction is sent to Instruction register from memory, prior to execution. So it is the temporary store for the current instruction of a program. Decoder, then decodes or interprets the instruction.

#### Timing and control unit

This unit synchronizes all the microprocessor operations with the clock and generates the control signals necessary for communication between the microprocessor and peripherals.

## **Interrupt control**

8085 microprocessor has 5 interrupts used to interrupt a program execution. They are

INTR, RST5.5, RST6.5, RST7.5, TRAP. TRAP is a non maskable interrupt and other interrupts are maskable.

#### Serial I/O control

8085 microprocessor has 2 signals SID and SOD to implement the serial transmission.

(i) SID-Serial Input Data line SOD-Serial Output Data line

Architecture details of 8085 Microprocessor

# Program 1

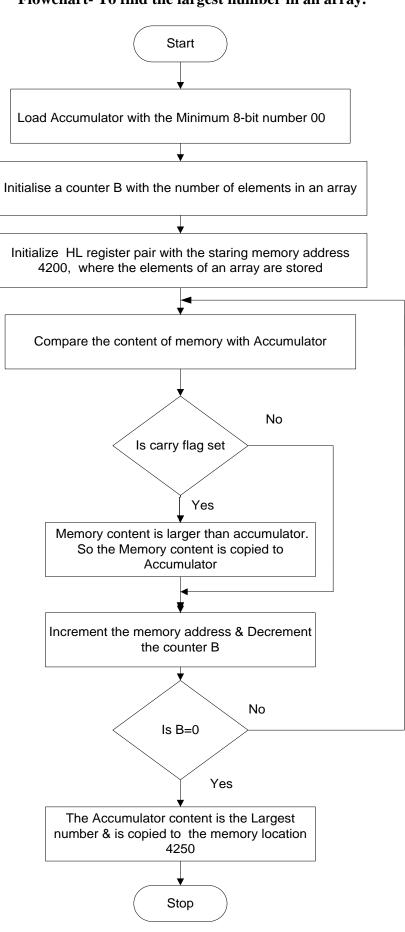

# To find the largest number in an array.

| ADDRESS | LABEL  | OPCODE | MNEMONICS   | COMMENTS                                          |

|---------|--------|--------|-------------|---------------------------------------------------|

|         | LINDLL | OLCODE |             |                                                   |

| 4100    |        |        | MVI A,00    | Move the Accumulator with the smallest 8 bit      |

|         |        |        |             | number 00                                         |

| 4102    |        |        | MVI B,05    | Initialize the B register as counter with the     |

|         |        |        |             | array size                                        |

| 4104    |        |        | LXI H, 4200 | Load HL register pair with the memory address     |

|         |        |        |             | 4200                                              |

| 4107    | LOOP1  |        | CMP M       | Compare the content of memory with                |

|         |        |        |             | Accumulator                                       |

| 4108    |        |        | JNC LOOP    | Jump on no carry to the memory address            |

|         |        |        |             | specified by the label LOOP                       |

| 410B    |        |        | MOV A,M     | Move the bigger number available in memory        |

|         |        |        |             | to Accumulator                                    |

| 410C    | LOOP   |        | INX H       | Increment HL register pair                        |

| 410D    |        |        | DCR B       | Decrement B register                              |

| 410E    |        |        | JNZ LOOP1   | If the B register is not equal to zero, then jump |

|         |        |        |             | to the memory address specified by the label      |

|         |        |        |             | LOOP1                                             |

| 4111    |        |        | STA 4250    | Store the Accumulator content (i.e. the largest   |

|         |        |        |             | number) in the memory address 4250                |

| 4114    |        |        | HLT         | Halt                                              |

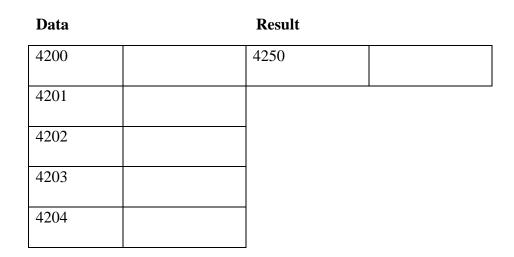

| Data | Result |  |

|------|--------|--|

| 4200 | 4250   |  |

| 4201 |        |  |

| 4202 |        |  |

| 4203 |        |  |

| 4204 |        |  |

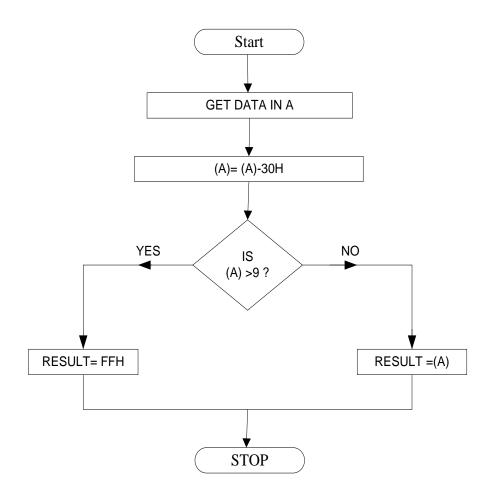

Flowchart- To find the largest number in an array.

# Program 2

# To find the smallest number in an array.

|         |       |        | 1           |                                                                                                            |

|---------|-------|--------|-------------|------------------------------------------------------------------------------------------------------------|

| ADDRESS | LABEL | OPCODE | MNEMONICS   | COMMENTS                                                                                                   |

| 4100    |       |        | MVI A,FF    | Move the Accumulator with the largest 8 bit<br>number FF                                                   |

| 4102    |       |        | MVI B,05    | Initialize the B register as counter with the array size                                                   |

| 4104    |       |        | LXI H, 4200 | Load HL register pair with the memory address<br>4200                                                      |

| 4107    | LOOP1 |        | СМР М       | Compare the content of memory with<br>Accumulator                                                          |

| 4108    |       |        | JC LOOP     | Jump on carry to the memory address specified<br>by the label LOOP                                         |

| 410B    |       |        | MOV A,M     | Move the smaller number available in memory<br>to Accumulator                                              |

| 410C    | LOOP  |        | INX H       | Increment HL register pair                                                                                 |

| 410D    |       |        | DCR B       | Decrement B register                                                                                       |

| 410E    |       |        | JNZ LOOP1   | If the B register is not equal to zero, then jump<br>to the memory address specified by the label<br>LOOP1 |

| 4111    |       |        | STA 4250    | Store the Accumulator content (i.e. the smallest<br>number) in the memory address 4250                     |

| 4114    |       |        | HLT         | Halt                                                                                                       |

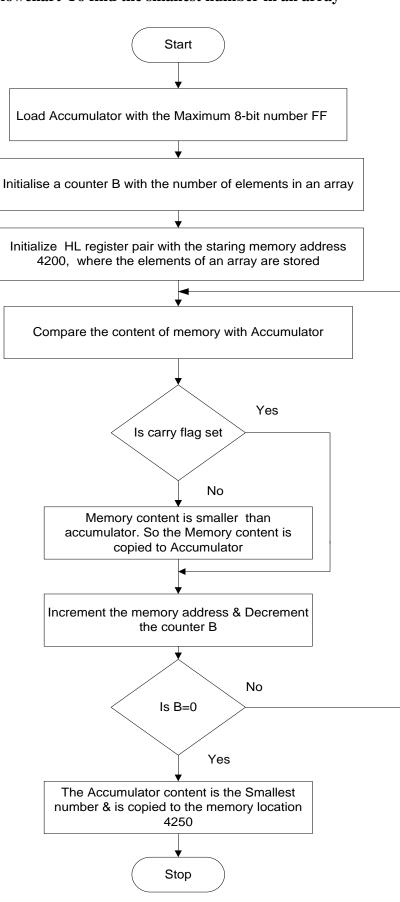

#### Flowchart-To find the smallest number in an array

# Program 3

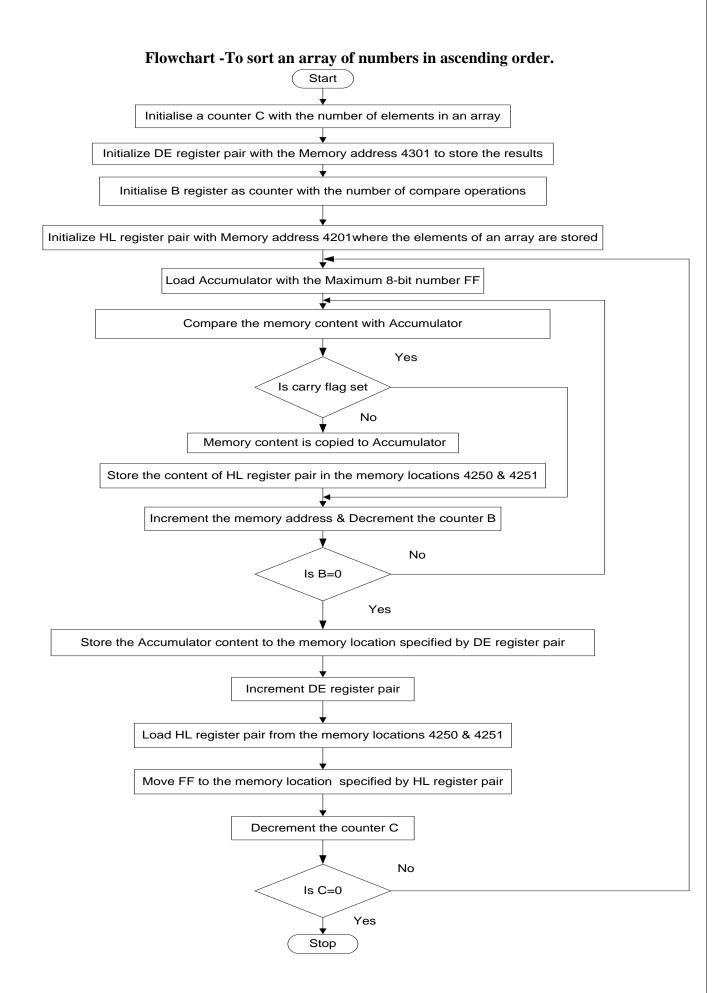

# To sort an array of numbers in ascending order.

| ADDRESS | LABEL | OPCODE | MNEMONICS   | COMMENTS                                                                                                   |

|---------|-------|--------|-------------|------------------------------------------------------------------------------------------------------------|

| 4100    |       |        | MVI C,05    | Initialize the C register as counter with the array size                                                   |

| 4102    |       |        | LXI D, 4301 | Load DE register pair with the memory<br>address 4301                                                      |

| 4105    | LOOP2 |        | MVI B,05    | Initialize the B register as counter with the number of compare operations                                 |

| 4107    |       |        | LXI H, 4201 | Load HL register pair with the memory<br>address 4201                                                      |

| 410A    |       |        | MVI A,FF    | Move the Accumulator with the largest 8<br>bit number FF                                                   |

| 410C    | LOOP1 |        | CMP M       | Compare the content of memory with<br>Accumulator                                                          |

| 410D    |       |        | JC LOOP     | Jump on carry to the memory address specified by the label LOOP                                            |

| 4110    |       |        | MOV A,M     | Move the smaller number available in memory to Accumulator                                                 |

| 4111    |       |        | SHLD 4250   | Store HL register pair in 4250 & 4251                                                                      |

| 4114    | LOOP  |        | INX H       | Increment HL register pair                                                                                 |

| 4115    |       |        | DCR B       | Decrement B register                                                                                       |

| 4116    |       |        | JNZ LOOP1   | If the B register is not equal to zero, then<br>jump to the memory address specified by<br>the label LOOP1 |

| 4119    |       |        | STAX D      | Store the Accumulator content (i.e. the<br>smallest number) in the memory address<br>4250                  |

| 411A    |       |        | INX D       | Increment HL register pair                                                                                 |

| 411B    |       |        | LHLD 4250   | Load HL register pair from 4250 & 4251                                                                     |

| 411E | MVI M, FF | Move FF to memory location where the smallest number is located                                            |

|------|-----------|------------------------------------------------------------------------------------------------------------|

| 4120 | DCR C     | Decrement C register                                                                                       |

| 4121 | JNZ LOOP2 | If the C register is not equal to zero, then<br>jump to the memory address specified by<br>the label LOOP2 |

| 4124 | HLT       | Halt                                                                                                       |

# Data

| 4201 |  |

|------|--|

| 4202 |  |

| 4203 |  |

| 4204 |  |

| 4205 |  |

# Result

| 4301 |  |

|------|--|

| 4302 |  |

| 4303 |  |

| 4304 |  |

| 4305 |  |

# Program 4

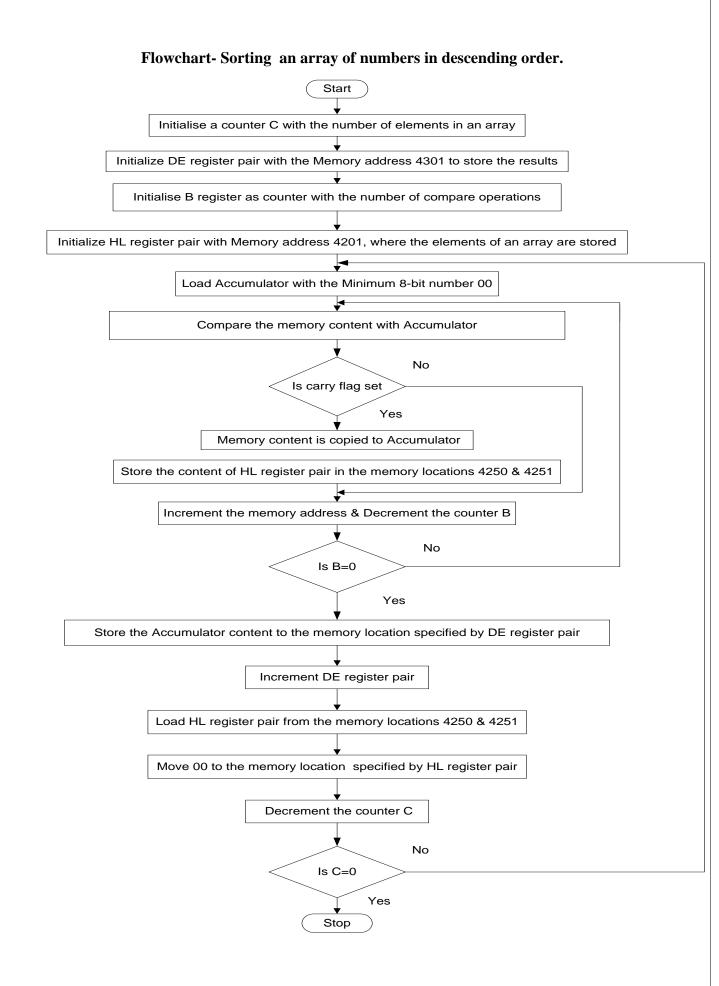

# To sort an array of numbers in descending order.

| ADDRESS | LABEL  | OPCODE | MNEMONICS   | COMMENTS                                                                                                   |

|---------|--------|--------|-------------|------------------------------------------------------------------------------------------------------------|

| 4100    |        |        | MVI C,05    | Initialize the C register as counter with the array size                                                   |

| 4102    |        |        | LXI D, 4301 | Load DE register pair with the memory<br>address 4301                                                      |

| 4105    | LOOP2: |        | MVI B,05    | Initialize the B register as counter with the number of compare operations                                 |

| 4107    |        |        | LXI H, 4201 | Load HL register pair with the memory<br>address 4201                                                      |

| 410A    |        |        | MVI A,00    | Move the Accumulator with the smallest<br>8 bit number 00                                                  |

| 410C    | LOOP1: |        | СМР М       | Compare the content of memory with<br>Accumulator                                                          |

| 410D    |        |        | JNC LOOP    | Jump on no carry to the memory address specified by the label LOOP                                         |

| 4110    |        |        | MOV A,M     | Move the smaller number available in memory to Accumulator                                                 |

| 4111    |        |        | SHLD 4250   | Store HL register pair in 4250 & 4251                                                                      |

| 4114    | LOOP:  |        | INX H       | Increment HL register pair                                                                                 |

| 4115    |        |        | DCR B       | Decrement B register                                                                                       |

| 4116    |        |        | JNZ LOOP1   | If the B register is not equal to zero, then<br>jump to the memory address specified by<br>the label LOOP1 |

| 4119    |        |        | STAX D      | Store the Accumulator content (i.e. the<br>smallest number) in the memory address<br>4250                  |

| 411A    |        |        | INX D       | Increment HL register pair                                                                                 |

| 411B    |        |        | LHLD 4250   | Load HL register pair from 4250 & 4251                                                                     |

| 411E | MVI M, 00 | Move 00 to memory location where the largest number is located                                             |

|------|-----------|------------------------------------------------------------------------------------------------------------|

| 4120 | DCR C     | Decrement C register                                                                                       |

| 4121 | JNZ LOOP2 | If the C register is not equal to zero, then<br>jump to the memory address specified by<br>the label LOOP2 |

| 4124 | HLT       | Halt                                                                                                       |

# Data

| 4201 |  |

|------|--|

| 4202 |  |

| 4203 |  |

| 4204 |  |

| 4205 |  |

# Result

| 4301 |  |

|------|--|

| 4302 |  |

| 4303 |  |

| 4304 |  |

| 4305 |  |

# Result

The above programs were executed and their results are verified using 8085 microprocessor.

### EX.NO:

#### **DATE:**

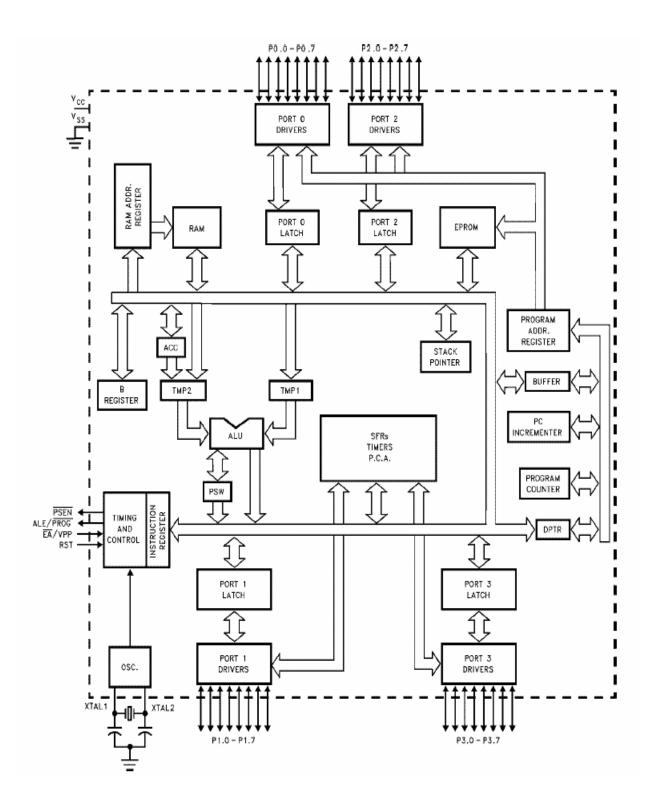

# **STUDY OF MICROCONTROLLER-8051**

### AIM:

To perform various arithmetic operations using 8051 microcontroller.

#### **THEORY:**

It is 8-bit microcontroller, means MC 8051 can Read, Write and Process 8 bit data. This is mostly used microcontroller in the robotics, home appliances like mp3 player, washing machines, electronic iron and industries. Mostly used blocks in the architecture of 8051 are as follows:

MC 8051 has 128 byte Random Access memory for data storage. Random access memory is non volatile memory. During execution for storing the data the RAM is used. RAM consists of the register banks, stack for temporary data storage. It also consists of some special function register (SFR) which are used for some specific purpose like timer, input output ports etc. Normally microcontroller has 256 byte RAM in which 128 byte is used for user space which is normally Register banks and stack. But other 128 byte RAM which consists of SFRs.

In 8051, 4KB read only memory (ROM) is available for program storage. This is used for permanent data storage. This is volatile memory; the data saved in this memory does not disappear after power failure.

#### **Timers and Counters**

Timer means which can give the delay of particular time between some events. For example on or off the lights after every 2 sec. This delay can be provided through some assembly program but in microcontroller two hardware pins are available for delay generation. • In MC8051, two timer pins are available T0 and T1, by these timers we can give the delay of particular time if we use these in timer mode and can count external pulses at these pins if we use these pins in counter mode.

• 16 bits timers are available. Means we can generate delay between 0000H to FFFFH.

- Two special function registers are available.

- TMOD, TCON registers are used for controlling timer operation.

### **Serial Port**

• There are two pins available for serial communication TXD and RXD. Normally TXD is used for transmitting serial data which is in SBUF register, RXD is used for receiving the serial data. SCON register is used for controlling the operation.

#### Oscillator

• It is used for providing the clock to MC8051 which decides the speed or baud rate of MC. The use of crystal which frequency vary from 4MHz to 30 MHz. There are four input output ports available P0, P1, P2, P3.

# Interrupts

• Interrupts are defined as requests because they can be refused (masked) if they are not used, that is when an interrupt is acknowledged. A special set of events or routines are followed to handle the interrupts. These special routines are known as interrupt handler or interrupt service routines (ISR). These are located at a special location in memory. INTO and INT1 are the pins for external interrupts.

# 8051 Flag Bits and PSW Register

$\rightarrow$  Used to indicate the Arithmetic condition of ACC.

$\rightarrow$  Flag register in 8051 is called as program status word (PSW). This special function register PSW is also bit addressable and 8 bit wide means each bit can be set or reset independently.

There are four flags in 8051

Parity flag

• overflow flag

• Auxiliary carry

• carry flag

$\rightarrow$  Four Register Banks

• RS1(PSW0.4) RS0(PSW0.3)

**Register Bank Select**

- 0 0 Bank 0

- 0 1 Bank 1

- 1 0 Bank 2

- 1 1 Bank 3

•  $F0 \rightarrow$  user definable bit

Stack is last in first out (LIFO)

# DPTR

It is a 16 bit register, it is divided into two parts DPH and DPL. DPH for Higher order 8 bits, DPL for lower order 8 bits. DPTR, DPH, DPL these all are SFRs in 8051.

# **PROCEDURE:**

- 1. Enter Opcode and data in trainer.

- 2. Execute the program.

- 3. Change the data and see that correct results are obtained.

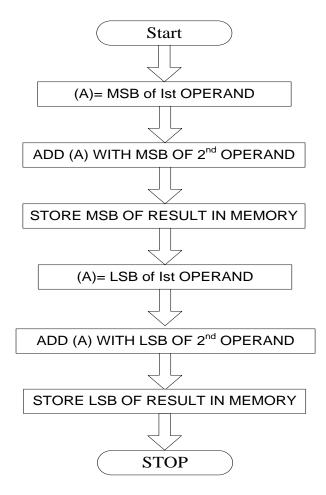

### **16 Bit Addition**

### A) ARITHMETIC OPERATIONS

### **PROGRAM 1: 16 Bit Addition**

#### **OBJECTIVE:**

To perform 16 bit addition of two 16-bit data using immediate addressing mode and store the result in memory.

#### **THEORY:**

As there is only one 16-bit register in 8051. 16-bit addition is performed by using ADDC instruction twice, i.e. addition LSD first and MSD next. This program adds the 16bit data 1234 with 5678 and store the result in 4150 and 4151 using immediate addressing.

#### **Program1:16 Bit Addition**

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS                                    |

|---------|-------|--------|-----------------|---------------------------------------------|

| 8100    |       |        | CLR C           | Clear cy flag                               |

| 8101    |       |        | MOV A,#DATA1    | Move Data 1 to A reg                        |

| 8103    |       |        | ADD A, #DATA2   | Add Data 2 with A Reg                       |

| 8105    |       |        | MOVDPTR,#8150   | Move 8150 to DPTR                           |

| 8108    |       |        | MOVX@DPTR, A    | Move LSB Result from<br>accumulator to DPTR |

| 8109    |       |        | INC DPTR        | Increment DPTR                              |

| 810A    |       |        | MOV A,# DATA M1 | Move MSB Data 1 to A reg                    |

| 810C    |       |        | ADDC,# DATA M2  | Add MSB Data 2 with A Reg<br>and CY flag.   |

| 810E    |       |        | MOVX@DPTR,A     | Move MSB Result from<br>accumulator to DPTR |

| 810F    | HERE  |        | SJMP HERE       | Short Jump                                  |

#### DATA:

8102: 34, 8104:78, 810B:12, 810D: 56

#### **RESULT:**

8150: AC; 8151:68

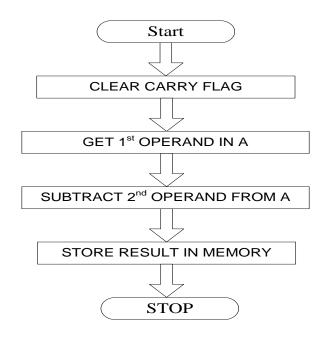

#### **PROGRAM 2: 8 BIT SUBTRACTION**

#### **OBJECTIVE:**

To perform subtraction of two 8 bit data using immediate addressing mode and store the result in memory.

### **8 BIT SUBTRACTION**

#### **8 BIT MULTIPLICATION**

#### **THEORY:**

Using the accumulator, subtraction is performed and results are stored. Immediate addressing is employed. The SUBB instruction write the result in the ACC.

## **Program 2: 8 Bit Subtraction**

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS                                |

|---------|-------|--------|-----------------|-----------------------------------------|

| 8100    |       |        | CLR C           | Clear cy flag                           |

| 8101    |       |        | MOV A,#DATA1    | Move Data 1 to A reg                    |

| 8103    |       |        | SUBB A,#DATA2   | SUB Data 2 with A Reg.                  |

| 8105    |       |        | MOV DPTR, #8500 | Move 8500 to DPTR                       |

| 8108    |       |        | MOVX @DPTR, A   | Move Result from<br>accumulator to DPTR |

| 8109    | HERE  |        | SJMP HERE       | Short Jump                              |

#### DATA:

8102: 20, 8104:10

#### **RESULT:**

8500: 10

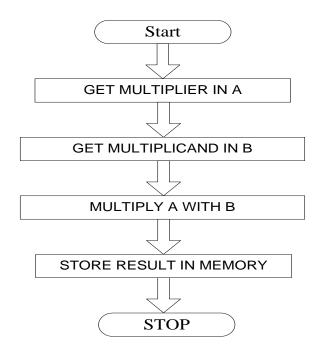

# **PROGRAM 3: 8 BIT MULTIPLICATION**

#### **OBJECTIVE:**

To obtain the product of two 8bit data using immediate addressing and store the result in memory.

### **THEORY:**

The 8051 microcontroller has MUL instruction unlike many other microprocessors. The MUL instruction multiplies the unsigned integers in A and B. The low order byte of the product is left in A and higher byte in B. If the product is greater than 255, the overflow flag is set, otherwise it is cleared. Carry flag is always cleared.

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS               |

|---------|-------|--------|-----------------|------------------------|

| 8100    |       |        | MOV A,#DATA1    | Move Data 1 to A reg   |

| 8102    |       |        | MOV B,#DATA2    | Move Data 2 to B reg   |

| 8105    |       |        | MUL AB          | MUL B Reg. with A Reg. |

| 8106    |       |        | MOV DPTR, #8500 | Move 8500 to DPTR      |

### **Program3: 8 Bit Multiplication**

# **8 BIT DIVISION**

| 8109 |      | MOVX @DPTR,A  | Move Result from<br>accumulator to DPTR |

|------|------|---------------|-----------------------------------------|

| 810A |      | INC DPTR      | Increment DPTR                          |

| 810B |      | MOV A,B       | Move B Reg. Result to A Reg.            |

| 010D |      |               | Move D Reg. Result to A Reg.            |

| 810D |      | MOVX @DPTR, A | Move Result from accumulator to DPTR    |

| 810E | HERE | SJMP HERE     | Short Jump                              |

## DATA:

8101: 0A, 8105:07

### **RESULT:**

8500: 46; 8501:00

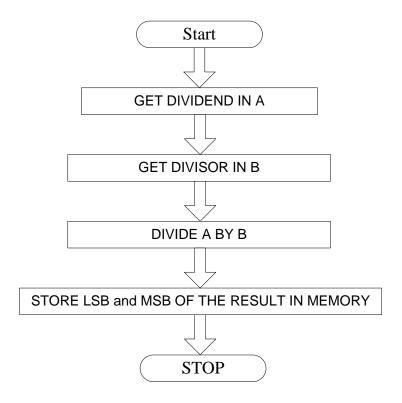

## **PROGRAM 4: 8 BIT DIVISION**

### **OBJECTIVE:**

To divide a 8 bit number by another 8bit number and to store the quotient and remainder in memory.

## **THEORY:**

The 8051 microcontroller has DIV instruction unlike any other 8bit microprocessors DIV instruction divides the unsigned 8bit integer in A by that in B. The ACC receives the integer part of the quotient and B receives the integer remainder. The carry and overflow flags will be cleared.

### **Program 4: 8 Bit Division**

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS                |

|---------|-------|--------|-----------------|-------------------------|

| 8100    |       |        | MOV A,#DATA1    | Move Data 1 to A reg    |

|         |       |        |                 |                         |

| 8102    |       |        | MOV B,#DATA2    | Move Data 2 to B reg    |

|         |       |        |                 |                         |

| 8105    |       |        | DIV AB          | DIV A Reg. by B Reg.    |

|         |       |        |                 |                         |

| 8106    |       |        | MOV DPTR, #8500 | Move 8500 to DPTR       |

|         |       |        |                 |                         |

| 8109    |       |        | MOVX @DPTR,A    | Move Result from        |

|         |       |        |                 | accumulator to DPTR     |

| 810A    |       |        | INC DPTR        | Increment DPTR          |

| 810B    |       |        | MOV A,B         | Move B Reg. Result to A |

|         |       |        |                 | Reg.                    |

| 810D    |       |        | MOVX @DPTR, A   | Move Result from        |

|         |       |        |                 | accumulator to DPTR     |

| 810E    | HERE  |        | SJMP HERE       | Short Jump              |

**DATA:** 8101: 65, 8104:0A

# RESULT: 8500: 0C (Quotient); 8501:05(Remainder)

#### **RESULT:**

Thus the various arithmetic operations were performed and verified using 8051 Microcontroller.

# ASCII TO DECIMAL CONVERSION

# **B) CODE CONVERSION USING 8051 MICROCONTROLLER**

## AIM:

To write and execute a few code conversion programs using 8051 microcontroller.

# **THEORY:**

Code conversion is very essential in micro computing because many peripherals that are to be dealt which may provide data in ASCII, BCD or various special codes. Each one of the special codes which is different from the binary concept of 8051 must be converted first to binary, for the microprocessor to process it. After processing, the binary form must again be converted back to the special code of that peripheral, before transferring it to the peripheral.

## **PROGRAM 1: ASCII TO DECIMAL CONVERSION**

**OBJECTIVE:** To convert the ASCII number in the accumulator to its equivalent decimal number.

**THEORY:** Conversion of an ASCII number t decimal is very simple because all the decimal numbers form a sequence in ASCII. Any ASCII number can be converted to decimal just by subtracting 30 from it.

| ADDRESS        | LABEL | OPCODE | MNEMONICS       | COMMENTS                                |  |

|----------------|-------|--------|-----------------|-----------------------------------------|--|

| 8100           |       |        | MOV DPTR, #8500 | Move 8500 to DPTR                       |  |

| 8103           |       |        | MOV A, #DATA    | Move data to A reg.                     |  |

| 8105           |       |        | CLR C           | Clear CY flag                           |  |

| 8106           |       |        | SUBB A, #30     | Sub 30 from A reg.                      |  |

| 8108           |       |        | CLR C           | Clear CY flag                           |  |

| 8109           |       |        | SUBB A,#0A      | Sub 0A from A reg. with borrow          |  |

| 810B           |       |        | JC STR          | Jump carry to STR                       |  |

| 810D           |       |        | MOV A,#0FF      | Move FF to A reg.                       |  |

| 810F           |       |        | SJMP L1         | SJMP to L1                              |  |

| 8111           | STR:  |        | ADD A, #0A      | Add 0A with A reg.                      |  |

| 8113           | L1:   |        | MOVX @DPTR,A    | Move Result from<br>accumulator to DPTR |  |

| 8114           | HLT:  |        | SJMP HLT        | Short Jump                              |  |

| Data: 35       | 1     |        | ata: 3B         | <u> </u>                                |  |

| Result [8500]: |       |        | Result [8500]:  |                                         |  |

# **Program 1: ASCII TO DECIMAL CONVERSION**

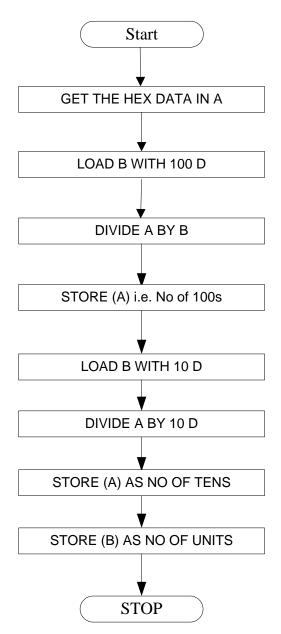

## HEX TO DECIMAL CONVERSION

### **PROGRAM 2: HEX TO DECIMAL CONVERSION**

**OBJECTIVE:** To obtain the decimal equivalent of an 8 bit hex number stored in memory.

**THEORY:** The Hex number is converted to its equivalent decimal number. The Hex number to be converted is brought to the accumulator and is divided by 100 D to find the number of hundreds in it. DIV instruction of 8051 is used in this program. The remainder is divided by 10 D to count the number of tens in it. Finally the remainder obtained from the above division gives the number of units in the given Hex number. The result is stored in memory in the unpacked form.

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS                                |

|---------|-------|--------|-----------------|-----------------------------------------|

| 8100    |       |        | MOV DPTR, #8500 | Move 8500 to DPTR                       |

| 8103    |       |        | MOVX A,@DPTR    | Move data to A reg.                     |

| 8104    |       |        | MOV B,#64       | Move 64 to B reg.                       |

| 8107    |       |        | DIV AB          | Div A by B                              |

| 8108    |       |        | MOV DPTR, #8501 | Move 8501 to DPTR                       |

| 810B    |       |        | MOVX @DPTR,A    | Move data to A reg                      |

| 810C    |       |        | MOV AB          | Move B reg. to A reg.                   |

| 810E    |       |        | MOV B, #0A      | Move 0A to B reg.                       |

| 8111    |       |        | DIV AB          | Div A by B                              |

| 8112    |       |        | INC DPTR        | Increment DPTR                          |

| 8113    |       |        | MOVX @DPTR,A    | Move data to A reg                      |

| 8114    |       |        | INC DPTR        | Increment DPTR                          |

| 8115    |       |        | MOV A,B         | Move B reg. to A reg                    |

| 4118    |       |        | MOVX @DPTR,A    | Move Result from accumulator<br>to DPTR |

| 4119    | HLT:  |        | SJMP HLT        | Short Jump                              |

## **Program 2: HEX TO DECIMAL CONVERSION**

Data: [8500]: 0F Result [8501]: [8502]:

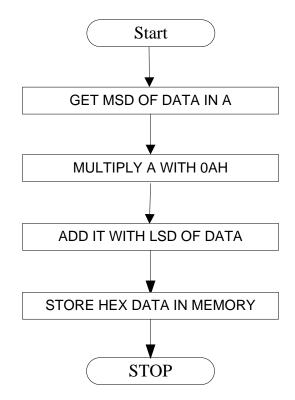

# **DECIMAL TO HEX CONVERSION**

### **PROGRAM 3: DECIMAL TO HEX CONVERSION**

**OBJECTIVE:** To convert BCD digits in memory to the equivalent hex number.

**THEORY:** Considering that out f the two unpacked BCD digits at 8500 and 8501, the digit at 8500 is the MSD, the logic is to multiply this by 0A (10D) and then add the LSD at 8501 to the product.

|         | LADEL | ODCODE | MNEMONICS       | COMMENTS                             |

|---------|-------|--------|-----------------|--------------------------------------|

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS                             |

| 8100    |       |        | MOV DPTR, #8500 | Move 8500 to DPTR                    |

| 8103    |       |        | MOVX A,@DPTR    | Move data to A reg.                  |

| 8104    |       |        | MOV B,#0AH      | Move 0A to B reg.                    |

| 8107    |       |        | MUL AB          | MUL A with B reg.                    |

| 8108    |       |        | MOV B,A         | Move A reg. B reg.                   |

| 810A    |       |        | INC DPTR        | Increment DPTR                       |

| 810B    |       |        | MOVX A,@DPTR    | Move DPTR content to A reg.          |

| 810C    |       |        | ADD A,B         | Add A reg. and B reg. content        |

| 810E    |       |        | INC DPTR        | Increment DPTR                       |

| 810F    |       |        | MOVX @DPTR,A    | Move Result from accumulator to DPTR |

| 8110    | HLT:  |        | SJMP HLT        | Short Jump                           |

### **Program 3: DECIMALTO HEX CONVERSION**

Data [8500]:03 [8501]:06

Result [8502]:

### **RESULT:**

Thus the above programs are loaded and the results are verified.

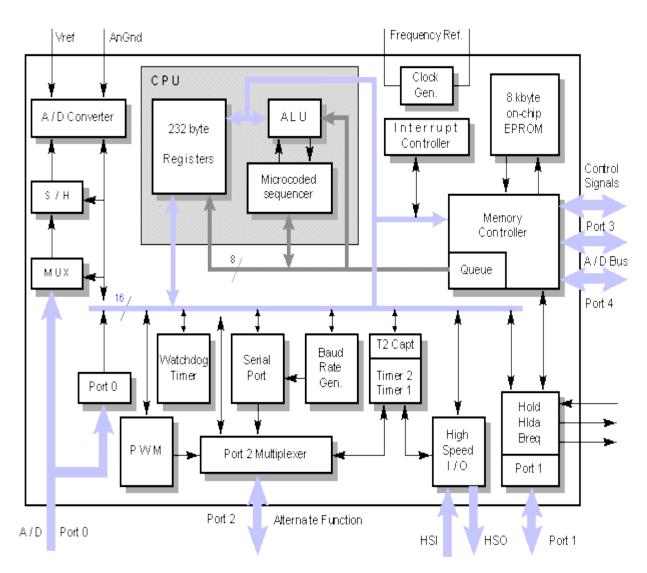

Architecture of 8097 Microcontroller

## **STUDY OF 8097 MICROCONTROLLER**

#### AIM

To perform various arithmetic and logical operations using 8097 microcontroller.

#### THEORY

Micro controllers are designed as a single chip, which typically includes a microprocessor, 64 bytes of Read/write memory, 8 Kbytes of ROM and several signal lines to connect I/O s. These are complete microcomputers on a chip also known as microcontroller. The features of 8097 are

- 1. A 8097 is a 16 bit microcontroller.

- 2. The 8097 is designed to use in applications which require high speed calculations and fast I/O operations.

- 3. The high speed I/O section of an 8097 includes a 16 bit timer, a 16 bit counter, a 4 input programmable edge detector, 4 software timers and a 6 output programmable event generator.

- 4. The 8097 has 8 multiplexed input analog to digital converter with 10 bit resolution. It can fully run under interrupt control.

- 5. Its programmable PWM output signals can be used as control signals to drive a motor and for any other applications.

- 6. Its several port has several modes of operation with programmable baud rates.

- 7. It supports register to register architecture which increases processing speed.

- 8. It has 100 instructions which can operate on bit, byte, word, double words.

- 9. It consists of a complete set of 16-bit arithmetic instructions including multiply and divide instructions.

- 10. Logical and arithmetic instructions are available for both byte and word operations.

- 11. The bit operations are possible and these can be performed on any bit in the register file or in the special function register.

The major components of the CPU on the 8097 are register file and the register ALU(RALU). The CPU register file has 256 bytes of memory. Out of 256 locations the first 24 memory locations 00H to 17H are the special function registers (SFRs). The SFRs are used to control the on chip I/O section. The upper 16 bytes of RAM is called power down RAM because these locations receive their power from the  $V_{PD}$  pin in the power down mode. RALU contains a 17 bit ALU, the program status word (PSW), the program counter (PC), a loop counter and three temporary registers.

The 8097 has two 16 bit timers. Timer 1 is used to synchronize events to real time, while timer 2 can be clocked externally and synchronizes events to external occurrences.

The high speed input unit (HIS), can be used to record the time at which an event occurs with respect to timer 1. The high speed output unit (HSO) is used to trigger events at specific times with minimal CPU overhead. These events include: starting an A to D conversion, resetting timer 2 setting 4 software flags and switching up to 6 output lines. The HSO can be

DATE:

programmed to generate interrupts at preset timers. The A/D converter on the 8097 provides 8input channels with a 10-bit digital output. The channels are multiplexed. Successive approximation technique is used for conversion.

There are five 8 bit I/O ports on 8097. Port 0 is an input only port which shares its pins with the analog inputs to the A/D converter. Port 1 is a quasi-bidirectional I/O port. Port 2 is a multifunctional port. Port 3 and port 4 pins have two functions. They are either bidirectional ports with open-drain outputs or system bus pins which the memory controller uses when it is accessing external memory.

The watchdog timer provides as a means of graceful recovery from a software upset. Once the watchdog is initialized if the software fails to reset the watchdog at least every 64K state times, a hardware reset will be initialized and the system will restart.

The addressable memory space on the 8097 consists of 64Kbytes. Locations 1FFEH and 1FFFH are reserved for ports 3 and 4 respectively. The 9 interrupt vectors are stored in locations 2000H through 2011H. 2012H through 207FH are reserved for Intel's factory test code. Resetting the 8097 causes instructions to be fetched starting from location 2080H. This location was chosen to allow a system to have up to 8K of RAM continuous with the register file. External memory is addressed through lines AD0- AD15 which forms a 16-bit multiplexed data bus. These lines share pins with I/O ports 3 and 4.

Eight interrupt sources are available on the 8097. Software trap, Extint, serial port, software timers, HSL0, high speed outputs, HIS data available, A/D conversion complete and timer overflow.

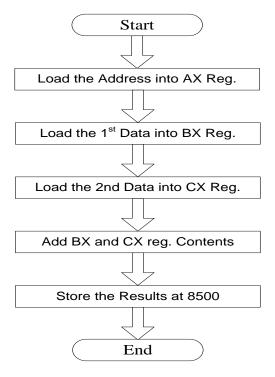

#### Program 1

#### Addition of Two 16-Bit Numbers

**Objective**: To add two16 bit hex numbers and store the result at 8500.

Data Reg 1: 0003-----0000 0000 0000 0011 Reg 2: 0007-----0000 0000 0000 0111

**Result** (8500): 0000 0000 0000 1010 (000A)

### Addition of Two 16-Bit Numbers

### Subtraction of Two 16-Bit Numbers

| Address | Opcodes | Mnemonics    | Comments                                             |

|---------|---------|--------------|------------------------------------------------------|

| 8100    |         | LD AX #8500H | Load AX with address 8500                            |

| 8104    |         | LD BX #0003H | Load BX with data 0003                               |

| 8108    |         | LD CX #0007H | Load CX with data 0007                               |

| 810C    |         | ADD BX,CX    | ADD BX and CX contents<br>and store the result in BX |

| 810F    |         | ST BX, [AX]+ | Store the result from BX to AX+                      |

| 8112    |         | SJMP HERE    | Short Jump                                           |

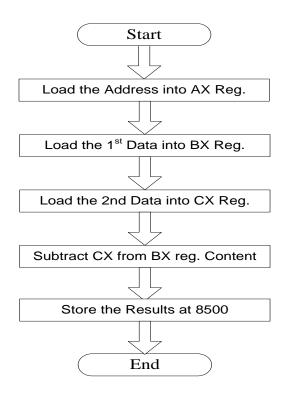

### Subtraction of Two 16-Bit Numbers

**Objective**: To subtract two16 bit hex numbers and store the result at 8500.

| Data   | Reg 1: 0007 | 0000 0000 0000 0111        |

|--------|-------------|----------------------------|

|        | Reg 1: 0003 | 0000 0000 0000 0011        |

| Result | 8500        | 0000 0000 0000 0100 (0004) |

| Address Opcodes |  | Mnemonics    | Comments                                          |  |

|-----------------|--|--------------|---------------------------------------------------|--|

| 8100            |  | LD AX #8500H | Load AX with address 8500                         |  |

| 8104            |  | LD BX #0007H | Load BX with data 0007                            |  |

| 8108            |  | LD CX #0003H | Load CX with data 0003                            |  |

| 810C            |  | SUB BX,CX    | SUB BX and CX contents and store the result in BX |  |

| 810F            |  | ST BX, [AX]+ | Store the result from BX to AX+                   |  |

| 8112            |  | SJMP HERE    | Short Jump                                        |  |

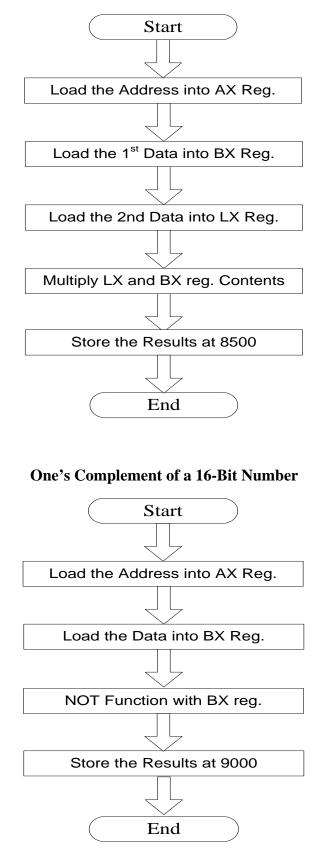

### Multiplication of Two 16-Bit Numbers

#### **Multiplication of Two 16-Bit Numbers**

**Objective**: To multiply two16 bit hex numbers and store the result at 8500.

Data Reg 1: 0007-----0000 0000 0000 0111

Reg 1: 0003-----0000 0000 0000 0011

**Result** (8500): 0000 0000 0001 0101 (0015)

| Address | Opcodes | Mnemonics    | Comments                                          |

|---------|---------|--------------|---------------------------------------------------|

| 8100    |         | LD AX #8500H | Load AX with address 8500                         |

| 8104    |         | LD BX #0007H | Load BX with data 0007                            |

| 8108    |         | LD CX #0003H | Load CX with data 0003                            |

| 810C    |         | MUL CX,BX    | MUL CX and BX contents and store the result in CX |

| 810F    |         | ST CL, [AX]+ | Store the result from CX to $AX+$                 |

| 8112    |         | ST CH, [AX]+ |                                                   |

| 8115    |         | SJMP HERE    | Short Jump                                        |

### **Program 4**

### **One's Complement of a 16-Bit Number**

**Objective**: To find the one's Complement of the 16 bit data in on chip register and store the result at 9000.

**Data** Reg BX: 1234-----0001 0010 0011 0100

**Result** (9000): 1110 1101 1100 1011 (EDCB)

| Address | Opcodes | Mnemonics    | Comments                       |

|---------|---------|--------------|--------------------------------|

| 8100    |         | LD AX #9000H | Load AX with address 9000      |

| 8104    |         | LD BX #1234H | Load BX with data 1234         |

| 8108    |         | NOT BX       | NOT the BX content             |

| 810A    |         | ST BX [AX]   | Store the result from BX to AX |

| 810D    |         | SJMP 820D    | Short Jump                     |

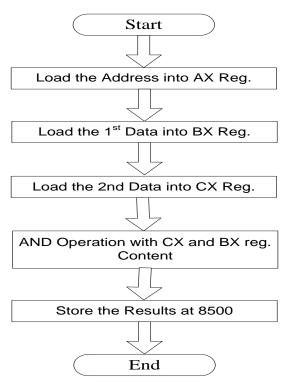

### AND Operation of Two 16-Bit Numbers

**OR Operation of Two 16-Bit Numbers**

#### **AND Operation of Two 16-Bit Numbers**

Objective: To discuss the usage of AND instruction

Data

Reg 1: 0003-----0000

0000

0011

Reg 2: 0007-----0000

0000

0000

0111

**Result** (8500): 0000 0000 0000 0011 (0003)

| Address | Opcodes | Mnemonics    | Comments                                          |

|---------|---------|--------------|---------------------------------------------------|

| 8100    |         | LD AX #8500H | Load AX with address 8500                         |

| 8104    |         | LD BX #0003H | Load BX with data 0003                            |

| 8108    |         | LD CX #0007H | Load CX with data 0007                            |

| 810C    |         | AND DX,CX,BX | AND BX and CX contents and store the result in DX |

| 8110    |         | ST DX, [AX]+ | Store the result from DX to AX+                   |

| 8113    |         | SJMP HERE    | Short Jump                                        |

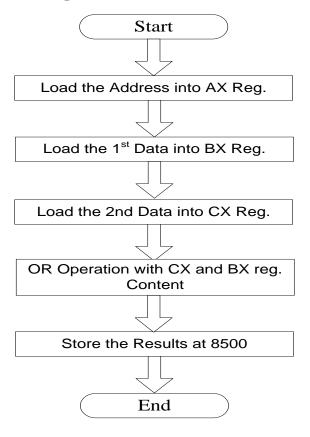

### **Program 6**

#### **OR** Operation of Two 16-Bit Numbers

Objective: To discuss the usage of OR instruction

Data Reg 1: 0003-----0000 0000 0000 0011 Reg 2: 0007-----0000 0000 0000 0111

Result (8500): 0000 0000 0000 0111 (0007)

| Address | Opcodes | Mnemonics    | Comments                                         |

|---------|---------|--------------|--------------------------------------------------|

| 8100    |         | LD AX #8500H | Load AX with address 8500                        |

| 8104    |         | LD BX #0003H | Load BX with data 0003                           |

| 8108    |         | LDCX #0007H  | Load CX with data 0007                           |

| 810C    |         | OR CX,BX     | OR BX and CX contents and store the result in CX |

| 8110    |         | ST CX, [AX]+ | Store the result from CX to AX+                  |

| 8113    |         | SJMP HERE    | Short Jump                                       |

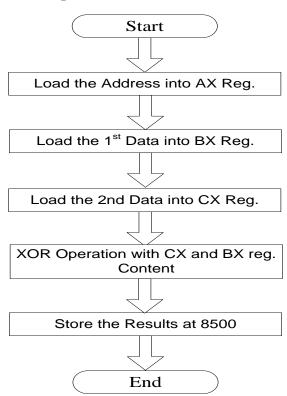

### **XOR Operation of Two 16-Bit Numbers**

### **XOR Operation of Two 16-Bit Numbers**

**Objective**: To discuss the usage of XOR instruction

**Data** Reg 1: 0003-----0000 0000 0000 0011

Reg 2: 0007-----0000 0000 0000 0111

**Result** (8500): 0000 0000 0100 (0004)

| Address | Opcodes | Mnemonics    | Comments                                          |

|---------|---------|--------------|---------------------------------------------------|

| 8100    |         | LD AX #8500H | Load AX with address 8500                         |

| 8104    |         | LD BX#0003H  | Load BX with data 0003                            |

| 8108    |         | LD CX #0007H | Load CX with data 0007                            |

| 810C    |         | XOR CX,BX    | XOR BX and CX contents and store the result in CX |

| 8110    |         | ST CX, [AX]+ | Store the result from CX to AX+                   |

| 8113    |         | SJMP HERE    | Short Jump                                        |

### **RESULT:**

Thus the various arithmetic and logical operations were performed and verified using 8097 microcontroller.

### EX.NO:

# **STUDY OF PROGRAMMABLE PERIPHERAL INTERFACE-8255**

#### AIM

To study the Input/ Output and BSR mode operations of 8255 interfaced with 8051 microcontroller.

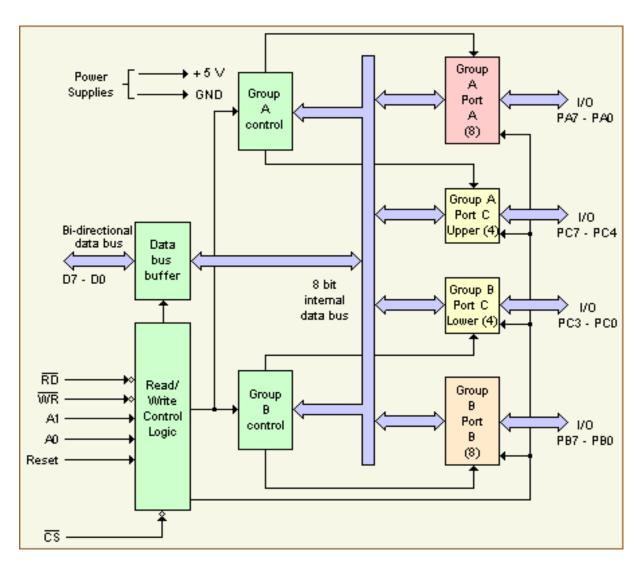

#### THEORY

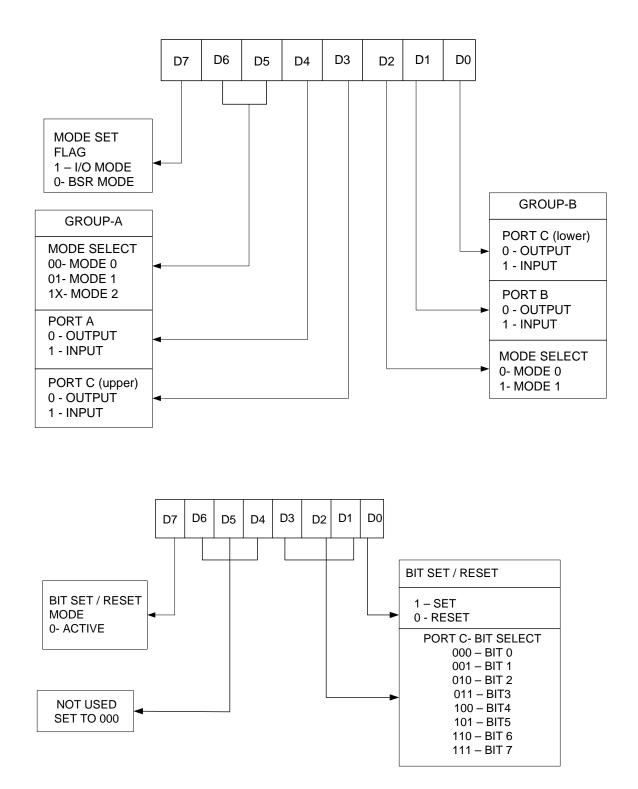

PPI is abbreviation for Programmable Peripheral Interface. It is an I/O port chip used for interfacing I/O devices with microprocessor. It is a very commonly used peripheral chip. It contains three 8 bit ports; Port A, Port B & Port C. Port C is composed of two independent 4-bit ports : PC7-4 (PC Upper) and PC3-0 (PC Lower). The three ports of 8255 are divided into two groups, Group A and Group B. Group A contains Port A (PA0 – PA7) and Port C higher order lines (PC4 – PC7). Group B contains Port B (PB0 – PB7) and Port C lower order lines (PC0 – PC3). Group A can be configured in three modes: mode-0, mode-1 & mode-2. Whereas Group B can configured in two modes: mode-0 and mode-1.

The ports are configured as input or output by the command word. The command word contains information such as mode, bit set, etc. i.e. the command word decides whether a Port is input Port or output Port and the mode of data transfer through a port. The command word is written into the control register of 8255. The control word of 8255 can only be written into, no read operation is allowed.

There are 3 modes of operation for the ports of 8255. Mode 0, Mode 1, and Mode 2.

#### **Read/Write control logic**

The function of this block is to manage all the internal and external transfer of both data and control or status word. The control pins with which the CPU communicates to 8255 are the RESET, CS, RD, WR, A0, A1, D0 – D7. Its basic operations are as given in the following table.

| RD      | - | Active low read        |

|---------|---|------------------------|

| WR      | - | Active low write       |

| CS      | - | Active low chip select |

| A0, A1  | - | Port address select    |

| D0 - D7 | - | Bidirectional data bus |

**Functional Block Diagram of 8255**

### Port address

The addresses for the four registers in the 8255 are:

| Register         | Address |

|------------------|---------|

| Control register | C6      |

| Port A           | C0      |

| Port B           | C2      |

| Port C           | C4      |

# Programming the 8255

There are 2 control words in 8255

- 1. Mode Definition (MD) Control word and

- 2. Bit Set / Reset (BSR) Control Word

# Program 1

To initialize port A as input port in mode0 & to input the data, set by the SPDT switches through

port A

| ADDRESS | LABEL | OPCODE | M    | NEMONICS       | COMMENTS                                        |

|---------|-------|--------|------|----------------|-------------------------------------------------|

| 4100    |       |        | MOV  | DPTR, # FFC6 H | FFC6-Address of the control register            |

| 4103    |       |        | MOV  | A, # 90 H      | Move the control word<br>to the accumulator     |

| 4105    |       |        | MOVX | @ DPTR, A      | Output the control word to the control register |

| 4106    |       |        | MOV  | DPTR, # FFC0 H | FFC0- Address of port<br>A. The data set by the |

| 4109    |       |        | MOVX | A, @ DPTR      | SPDT switch is moved to accumulator             |

| 410A    |       |        | MOV  | DPTR, # 4500 H | The accumulator value is stored to the memory   |

| 410D    |       |        | MOVX | @ DPTR, A      | location 4500                                   |

| 410E    | HERE  |        | SJMP | HERE           |                                                 |

### program 2

- To initialize port A as input port & port B as an output port in mode 0.

- To input the data, set by the SPDT switches through port A & to output the same data by the LEDs through port B.

| ADDRESS | LABEL | OPCODE | Ν    | INEMONICS      | COMMENTS                                             |

|---------|-------|--------|------|----------------|------------------------------------------------------|

| 4100    |       |        | MOV  | DPTR, # FFC6 H | FFC6-Address of the control register                 |

| 4103    |       |        | MOV  | A, # 90 H      | Move the control word to the accumulator             |

| 4105    |       |        | MOVX | @ DPTR, A      | Output the control word to the control register      |

| 4106    |       |        | MOV  | DPTR, # FFC0 H | FFC0- Address of port A.<br>The data set by the SPDT |

| 4109    |       |        | MOVX | A, @ DPTR      | switch is moved to accumulator                       |

| 410A    |       |        | MOV  | DPTR, # FFC2 H | FFC2- Address of port B.<br>The accumulator value is |

| 410D    |       |        | MOVX | @ DPTR, A      | send through port B to glow the LEDs.                |

| 410E    | HERE  |        | SJMP | HERE           |                                                      |

# **Program 3**

- To initialize port C as an output port in mode 0.

- To output the data through port C.

| ADDRESS | LABEL | OPCODE | M    | NEMONICS       | COMMENTS                                        |

|---------|-------|--------|------|----------------|-------------------------------------------------|

| 4100    |       |        | MOV  | DPTR, # FFC6 H | FFC6-Address of the control register            |

| 4103    |       |        | MOV  | A, # 90 H      | Move the control word to the accumulator        |

| 4105    |       |        | MOVX | @ DPTR, A      | Output the control word to the control register |

| 4106    |       |        | MOV  | DPTR, # FFC4 H | FFC4-Address of the port C                      |

| 4109    |       |        | MOV  | A, # 80        | Move the accumulator with data                  |

| 410B    |       |        | MOVX | @ DPTR, A      | To output the data through port C               |

| 410C    | HERE  |        | SJMP | HERE           |                                                 |

• To initialize port C as an input port in mode 0.

| ADDRESS | LABEL | OPCODE | MNEMONICS          | COMMENTS                                                 |

|---------|-------|--------|--------------------|----------------------------------------------------------|

| 4100    |       |        | MOV DPTR, # FFC6 H | FFC6-Address of the control register                     |

| 4103    |       |        | MOV A, # 99 H      | Move the control word to the accumulator                 |

| 4105    |       |        | MOVX @ DPTR, A     | Output the control word to the control register          |

| 4106    |       |        | MOV DPTR, # FFC4 H | FFC4-Address of the port C                               |

| 4109    |       |        | MOV A, @ DPTR      | Move the data from port C to accumulator                 |

| 410A    |       |        | MOV DPTR, # 4500 H | Move the accumulator content to the memory location 4500 |

| 410D    |       |        | MOVX @ DPTR, A     |                                                          |

| 410E    | HERE  |        | SJMP HERE          |                                                          |

# Result

The operation of 8255 in Input / Output mode has been studied and the results were verified.

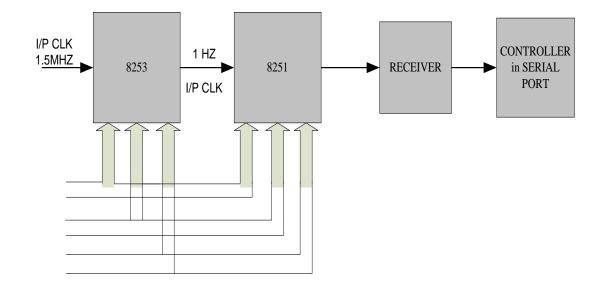

**Block Diagram of 8253-Programmable Interval Timer**

#### **Block Diagram of 8251-Programmable Communication Interface**

#### EX.NO:

#### DATE:

# SINGLE CHARACTER TRANSMISSION AND RECEPTION USING 8051 MICROCONTROLLER

#### AIM:

To initiate 8253 and 8251 and to check the transmission and reception of a character.

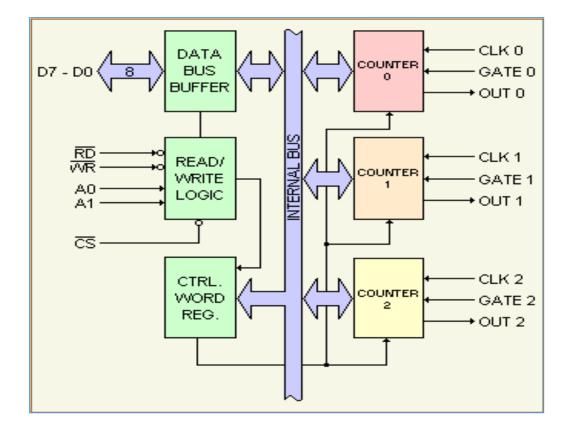

#### The Programmable Interval Timer/Counter – 8253:

The 8253 programmable Interval timer consists of three independent 16-bit programmable counters (timers). Each counter is capable of counting in binary or binary coded decimal. The maximum allowable frequency to any counter is 10MHz. This device is useful whenever the microprocessor must control real-time events. The timer in a personal computer is an 8253. To operate a counter a 16-bit count is loaded in its register and on command, it begins to decrement the count until it reaches 0. At the end of the count it generates a pulse, which interrupts the processor. The count can count either in binary or BCD.

**Data bus buffer-** It is a communication path between the timer and the microprocessor. The buffer is 8-bit and bidirectional. It is connected to the data bus of the microprocessor.

**Read** / write logic controls the reading and the writing of the counter registers.

Control word register, specifies the counter to be used and either a Read or a write operation.

| A1 | A0 | Selection |

|----|----|-----------|

| 0  | 0  | Counter 0 |

| 0  | 1  | Counter 1 |

| 1  | 0  | Counter 2 |

| 1  | 1  | Control   |

| I  | 1  | Register  |

Each counter in the block diagram has 3 logical lines connected to it. Two of these lines, clock and gate, are inputs. The third, labeled OUT is an output.

**Clock** - clock input for the counter. The counter is 16 bits. It provides the basic operating frequency to the timer. The maximum clock frequency is 1/380 nanoseconds or 2.6megahertz. **Out** – this is the output of the timer.

Gate – controls the timer. It's used either to enable or disable the counter.

The 8253 can operate independently in any one of the 6 modes. They are

Mode 0 Interrupt on terminal count

Mode 1 Programmable one shot

Mode 2 Rate Generator

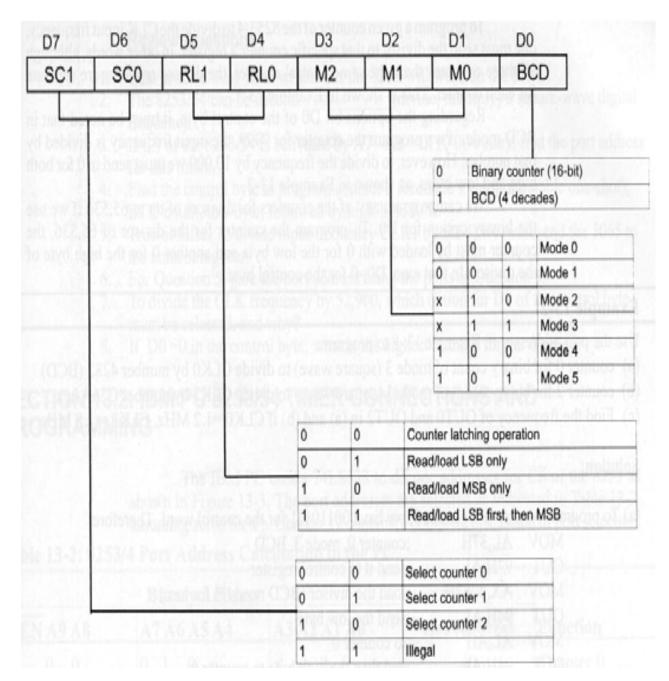

8253-Control Word Format

Mode 3 Square wave rate Generator

Mode 4 Software triggered strobe

Mode 5 Hardware triggered strobe

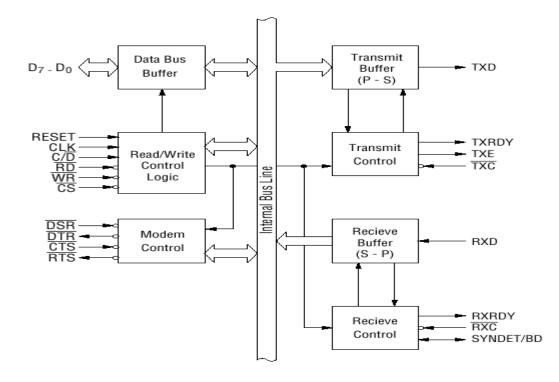

### Programmable Communication Interface-8251 (USART)

The 8251 is used as a peripheral device for serial communication and is programmed by the CPU to operate using virtually any serial data transmission technique. The USART accepts data characters from the CPU in parallel format and then converts them into a continuous serial data stream for transmission. Simultaneously, it can receive serial data streams and convert them into parallel data characters for the CPU. The CPU can read the status of USART at any time. These include data transmission errors and control signals. Prior to starting data transmission or reception, the 8251 must be loaded with a set of control words generated by the CPU. These control signals define the complete functional definition of the 8251 and must immediately follow a RESET operation. Control words should be written into the control register of 8251.

#### **Command Instruction Format:**

This format defines a status word that is used to control the actual operation of 8251. All control words written into 8251 after the mode instruction will load the command instruction. The command instructions can be written into 8251 at any time in the data block during the operation of the 8251. To return to the mode instruction format, the master reset bit in the command instruction word can be set to initiate an internal reset operation which automatically places the 8251 back into the mode instruction format. Command instructions must follow the mode instructions or sync characters.

There are two types of control word.

- 1. Mode instruction (setting of function)

- 2. Command (setting of operation)

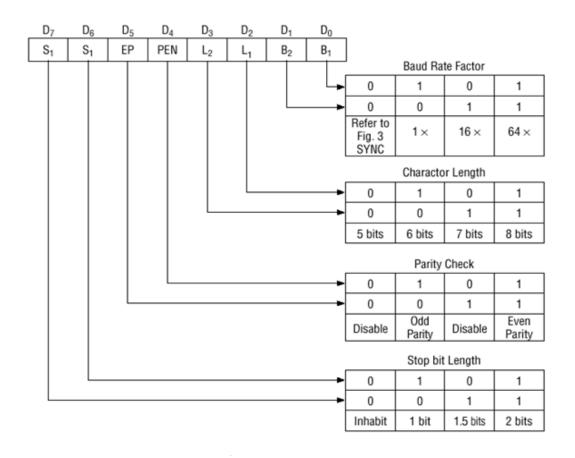

### 1) Mode Instruction

Mode instruction is used for setting the function of the 8251. Mode instruction will be in "wait for write" at either internal reset or external reset. That is, the writing of a control word after resetting will be recognized as a "mode instruction."

Items set by mode instruction are as follows:

- Synchronous/asynchronous mode

- Stop bit length (asynchronous mode)

- Character length

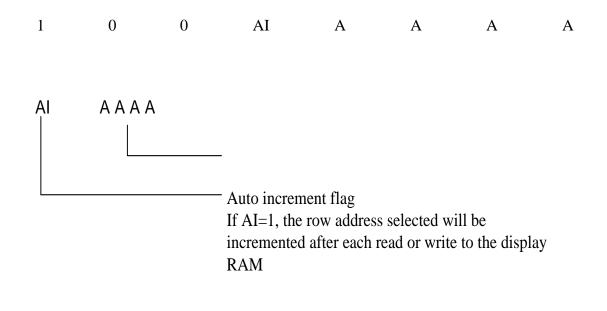

# 8251-Asynchronous Mode Instruction Format

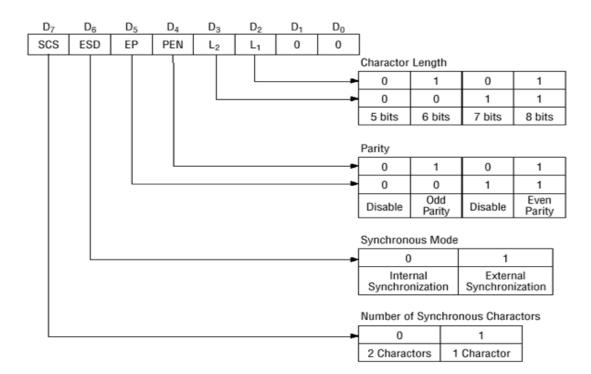

#### 8251-synchronous Mode Instruction Format

- Parity bit

- Baud rate factor (asynchronous mode)

- Internal/external synchronization (synchronous mode)

- Number of synchronous characters (Synchronous mode)

The bit configuration of mode instruction is shown in Figures 4 and 5. In the case of synchronous mode, it is necessary to write one-or two byte sync characters. If sync characters were written, a function will be set because the writing of sync characters constitutes part of mode instruction.

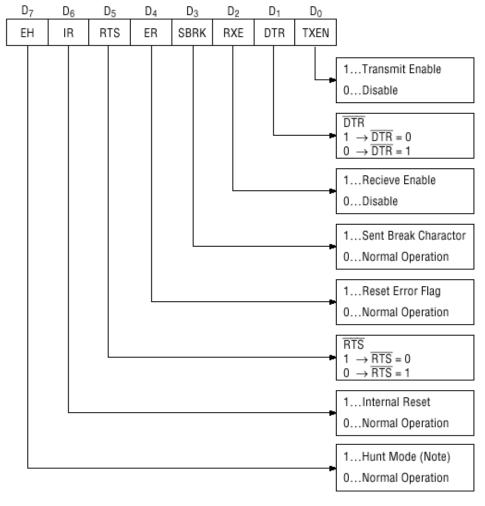

### 2) Command

Command is used for setting the operation of the 8251. It is possible to write a command whenever necessary after writing a mode instruction and sync characters. Items to be set by command are as follows:

- Transmit Enable/Disable

- Receive Enable/Disable

- DTR, RTS Output of data.

- Resetting of error flag.

- Sending to break characters

- Internal resetting

- Hunt mode (synchronous mode)

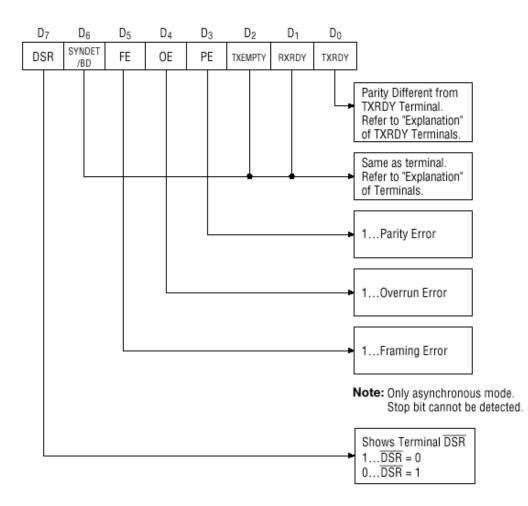

#### 3) Status Word

It is possible to see the internal status of the 8251 by reading a status word. The bit configuration of status word is shown in Fig. 7.

The following table gives the addresses of the peripheral.

| 8253 Control RegisterFFCE | 8253 Channel 0     | FFC8 |

|---------------------------|--------------------|------|

| 8253 Channel 1FFCA        | 8253 Channel 2     | FFCC |

| 8251 Control RegisterFFC2 | 8251 Data Register | FFC0 |

Note: Seach mode for synchronous charactors in synchronous mode.

Fig. 6: Bit Configuration of Command

| ADDRESS | LABEL | OPCODE | MNEMONICS       | COMMENTS                                                                                        |

|---------|-------|--------|-----------------|-------------------------------------------------------------------------------------------------|

| 8100    |       |        | MOV A,#36       | Channel 0 in mode 3                                                                             |

| 8102    |       |        | MOV DPTR, #FFCE | 8253-Control Reg. address                                                                       |

| 8105    |       |        | MOVX @DPTR,A    |                                                                                                 |

| 8106    |       |        | MOV A,#0A       | to get an output frequency of<br>150KHZ at ch-0, so as to get a<br>baud rate of 150KHZ at ch-0. |

| 8108    |       |        | MOV DPTR,#FFC8  | 8253-Control 0 address                                                                          |

| 810B    |       |        | MOVX@DPTR,A     |                                                                                                 |

| 810C    |       |        | MOV A,#00       |                                                                                                 |

| 810E    |       |        | MOVX @DPTR,A    |                                                                                                 |

| 810F    |       |        | MOV A,#4E       | 8251-Mode Command Word                                                                          |

| 8111    |       |        | MOV DPTR,#FFC2  | 8251-Control Reg. address                                                                       |

| 8114    |       |        | MOVX@DPTR,A     |                                                                                                 |

| 8115    |       |        | MOV A,#37       | 8251-Control Word                                                                               |

| 8117    |       |        | MOVX @DPTR,A    |                                                                                                 |

| 8118    |       |        | MOV A,#41       | Data                                                                                            |

| 811A    |       |        | MOV DPTR,#FFC0  | 8253-Data Reg. address                                                                          |

| 811D    |       |        | MOVX@DPTR,A     |                                                                                                 |

| 811E    |       |        | MOVX A,@DPTR    |                                                                                                 |

| 811F    |       |        | MOV DPTR,#8200  |                                                                                                 |

| 8122    |       |        | MOVX@DPTR,A     |                                                                                                 |

| 8123    | HERE: |        | SJMP HERE       |                                                                                                 |

# Program-To Check Transmission and Reception of a Character

### **RESULT:**

The program receives the character 41H and stores it at location 8200H.

Fig. 7: Bit Configuration of Status Word

# EX.NO:

# **DATE:**

# SEVEN SEGMENT LED DISPLAY USING 8051 MICROCONTROLLER

#### AIM

To develop programs for displaying fixed message and rolling message using 8051 Microcontroller.

#### THEORY

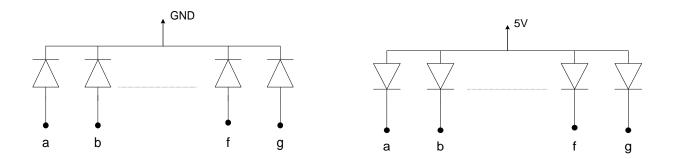

The seven segment display is the most commonly used, least expensive and the easiest to interface with the microprocessor. There are two types of seven segment displays

They are

(i) Common cathode display

(ii) Common anode display

**Common cathode display**

Common anode display

For a common anode display, a low is applied to a segment to turn it on. For a Common cathode display a high is applied to a segment to turn it on. In this board Common cathode display is used.

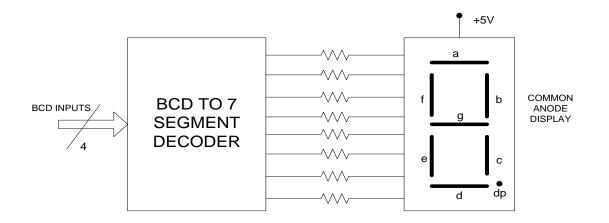

#### **Static Displays**

A seven segment display is driven by a BCD to seven segment driver / decoder. When the BCD input is sent to the inputs of the BCD-to-seven segment decoder, it outputs low on the segments required to display the number represented by the BCD code. This circuit is referred to as static display.

### **Disadvantages of Static Displays**

1. Power consumption is very high when more number of seven segment displays are used. The current required by the decoders and LED displays might be several times the current required by the rest of the circuitry in the instrument used.

2. Separate decoders are required for each seven segment display.

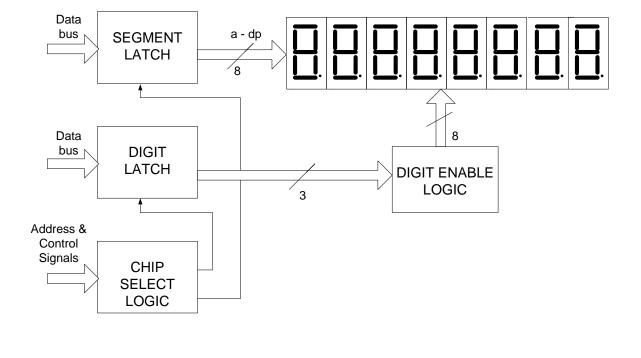

### **Multiplexed Displays**

To overcome the disadvantage of static displays, multiplexed displays are used. The trick of multiplexing displays is that the segment information is sent out to all of the digits on a common bus. But only one display is turned ON at a time, at which the information is displayed. So it is possible to display 8 information at different digits by simultaneously switching the data as well as the digit-location in a sequential order.

### Program 1

### To display a fixed message "HELLO"

VBMB-016 is used to display 8 digits of information using a simple software routine. The algorithm used in the software is as follows

- Select the most significant digit by issuing a suitable control word to the digit select port.

- Out the Hex code corresponding to the first digit information to the data port.

- Introduce a delay for atleast 2 msec.

- Select the second digit.

- Out second digit Hex code.

- Introduce delay for 2ms.

- Likewise repeat for all digits.

- After displaying the 8<sup>th</sup> digit, repeat from the first digit.

| ADDRESS | LABEL | OPCODE | MNEM | IONICS       | COMMENTS                    |

|---------|-------|--------|------|--------------|-----------------------------|

| 4100    | START |        | MOV  | DPTR, # 4200 | Move the data pointer with  |

|         |       |        |      |              | the memory address of the   |

|         |       |        |      |              | message to be displayed     |

| 4103    |       |        | MOV  | R2, DPL      |                             |

| 4105    | CON   |        | MOV  | R3, DPH      |                             |

|         |       |        |      |              |                             |

| 4107    |       |        | MOV  | R0, # 07     |                             |

| 4109    |       |        | MOV  | R7, # 08     | Initialize no. of digits to |

|         |       |        |      |              | scan                        |

| 410B    | L1    |        | MOV  | A, R0        | Select digit position       |

|         |       |        |      |              |                             |

| 410C    |       |        | MOV  | DPTR, # FFC0 |                             |

| 410F     |               |    |    |    | MOVX           | K @ D | PTR, A              | 4   |           |                                                                         |                        |  |

|----------|---------------|----|----|----|----------------|-------|---------------------|-----|-----------|-------------------------------------------------------------------------|------------------------|--|

| 4110     |               |    |    |    | MOV            | DPI   | 2, R2               |     | Ou        | it the H<br>rresponding t                                               | lex code               |  |

| 4112     |               |    |    |    | MOV            | DPH   | I, R3               |     | inf       | information to the data<br>port                                         |                        |  |

| 4114     |               |    |    |    | MOVX A, @ DPTR |       |                     |     |           |                                                                         |                        |  |

| 4115     |               |    |    |    | MOV            | DPT   | <sup>°</sup> R, # F | FC8 |           |                                                                         |                        |  |

| 4118     |               |    |    |    | MOVX           | K @ D | PTR, 2              | A   |           |                                                                         |                        |  |

| 4119     |               |    |    |    | LCALI          | L DEI | LAY                 |     |           | ll the delay                                                            | subroutine             |  |

| 411C     |               |    |    |    | INC            | R2    |                     |     | Sel       | lect the nex<br>crementing<br>inter                                     | t digit by<br>the data |  |

| 411D     |               |    |    |    | DEC R0         |       |                     |     |           | eck if 8<br>played, if                                                  |                        |  |

| 411E     |               |    |    |    | DJNZ R7, L1    |       |                     |     |           | om first digit                                                          |                        |  |

| 4120     |               |    |    |    | JMP            | STAI  | RT                  |     | dig       | After displaying the 8 <sup>th</sup> digit, repeat from the first digit |                        |  |

| 4122     | DELAY         |    |    |    | MOV            | R4,   | # 02                |     |           | 511                                                                     |                        |  |

| 4124     | L3            |    |    |    | MOV            | R5,   | # FF                |     | De<br>del | elay program                                                            | for 2 msec             |  |

| 4126     | L2            |    |    |    | DJNZ           | R5,   | L2                  |     |           | lay                                                                     |                        |  |

| 4128     |               |    |    |    | DJNZ           | R4,   | L3                  |     |           |                                                                         |                        |  |

| 412A     |               |    |    |    | RET            |       |                     |     |           |                                                                         |                        |  |

| Characte | er D7         | D6 | D5 | D4 | D3             | D2    | D1                  | D0  | Hex       | Address                                                                 |                        |  |

| H        | $\frac{D}{0}$ | 1  | 1  | 1  | 0              | 1     | 1                   | 0   | 76        | 4200                                                                    |                        |  |

| E        | 0             | 1  | 1  | 1  | 1              | 0     | 0                   | 1   | 79        | 4201                                                                    |                        |  |

|          | 0             | 0  | 1  | 1  | 1              | 0     | 0                   | 0   | 38        | 4202                                                                    |                        |  |

| L        | 0             | 0  | 1  | 1  | 1              | 0     | 0                   | 0   | 38        | 4203                                                                    |                        |  |

| 0        | 0             | 0  | 1  | 1  | 1              | 1     | 1                   | 1   | 3F        | 4204                                                                    |                        |  |

## Data - 0 to 7

| Character | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex | Address |

|-----------|----|----|----|----|----|----|----|----|-----|---------|

| 0         | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 3F  | 4200    |

| 1         | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 06  | 4201    |

| 2         | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 5B  | 4202    |

| 3         | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 4F  | 4203    |

| 4         | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 66  | 4204    |

| 5         | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 6D  | 4205    |

| 6         | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 7D  | 4206    |

| 7         | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 07  | 4207    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 4208    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 4209    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 420A    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 420B    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 420C    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 420D    |

| Blank     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00  | 420E    |

| 0         | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 3F  | 420F    |

| 1         | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 06  | 4210    |

| 2         | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 5B  | 4211    |

| 3         | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 4F  | 4212    |

| 4         | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 66  | 4213    |

| 5         | 0  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 6D  | 4214    |

| 6         | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 7D  | 4215    |

| 7         | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 07  | 4216    |

## Program 2

To display a Rolling message "0 to 7"

- This program displays a block of information (integers 0-7) in a rolling mode.

- The data are stored from memory location 4200. The contents of memory locations from 4200H must be as follows. First block from 4200-4207 is displayed, then 4201-4208 is displayed, likewise the message is left shifted and displayed.

| ADDRESS | LABEL | OPCODE | MN          | EMONICS     | COMMENTS                                                                           |

|---------|-------|--------|-------------|-------------|------------------------------------------------------------------------------------|

| 4100    | REP   |        | MOV         | R1, 0F      | Delay for rolling                                                                  |

| 4102    |       |        | MOV         | R4, 00      |                                                                                    |

| 4104    | CON   |        | MOV<br>4200 | DPTR, #     | Move the data pointer with<br>the memory address of the<br>message to be displayed |

| 4107    |       |        | MOV         | R2, DPL     |                                                                                    |

| 4109    |       |        | MOV         | R3, DPH     |                                                                                    |

| 410B    |       |        | MOV         | A, R4       |                                                                                    |

| 410C    |       |        | ADD         | A, R2       |                                                                                    |

| 410D    |       |        | MOV         | R2, A       |                                                                                    |

| 410E    |       |        | MOV         | R0, # 07    |                                                                                    |

| 4110    |       |        | MOV         | R7, # 08    | Initialize no. of digits to scan                                                   |

| 4112    | L5    |        | DEC         | R7          |                                                                                    |

| 4113    |       |        | MOV         | A, R0       | Select digit position                                                              |

| 4114    |       |        | MOV D       | PTR, # FFC0 |                                                                                    |

| 4117    |       |        | MOVX        | @ DPTR, A   |                                                                                    |

| 4118    |       |        | MOV         | DPH, R3     | Out the Hex code<br>corresponding to the digit                                     |

| 411A    |       |        | MOV         | DPL, R2     | information to the data port                                                       |

| 411C    |       |        | MOVX        | A, @ DPTR   |                                                                                    |

| 411D    |       |        | MOV D       | PTR, # FFC8 |                                                                                    |

| 4120 |       | MOVX       | @ DPTR, A    |                                                                    |